Tips & Tricks

Signaal verkorten to 1CC

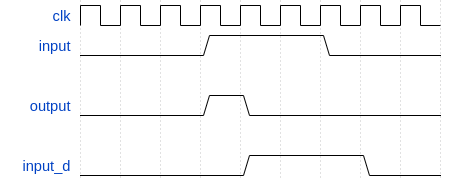

Soms is het handig om signalen te verkorten. Een stuursignaal kan, bijvoorbeeld, enkele clock cycles hoog zijn. De hardware echter verwacht een hoog signaal dat precies 1 clock cycle duurt.

Van zodra je begint te denken “nu moet dit zijn en daarvoor moest dat zijn … FF-tijd.

-- entity

-- architecture

signal input_d : STD_LOGIC;

-- begin

PREG: process(clock_i)

begin

if rising_edge(clock_i) then

input_d <= input_i;

end if;

end process;

output_i <= input_i AND not(input_d);

-- end architecture

‘Default’ waardes bij een MUX

Het is uiterst belangrijk dat bij een MUX ALLE outputs een waarde toegekend krijgen, voor elke mogelijke conditie!! Je kan jezelf beschermen van de zonde om dit te vergeten door te werken met een “default”-waarde.

Het voorbeeld hiernaast ziet er op het eerste zicht correct uit en volgens de VHDL syntax is dit ook zo. Afhankelijk van de laatste bit zal het signaal getal_is_even hoog worden, of getal_is_oneven.

Dit zijn eigenlijk twee muxen, die in één proces beschreven worden!!

-- entity

-- architecture

signal getal : STD_LOGIC_VECTOR(3 downto 0);

signal getal_is_even, getal_is_oneven : STD_LOGIC;

-- begin

PMUX: process(getal)

begin

if getal(0) = '1' then

getal_is_oneven <= '1';

elsif getal(0) = '0' then

getal_is_even <= '1';

end if;

end process;

-- end architecture

-- entity

-- architecture

signal getal : STD_LOGIC_VECTOR(3 downto 0);

signal getal_is_even, getal_is_oneven : STD_LOGIC;

-- begin

PMUX: process(getal)

begin

if getal(0) = '1' then

getal_is_oneven <= '1'; getal_is_even <= '0';

elsif getal(0) = '0' then

getal_is_oneven <= '0'; getal_is_even <= '1';

end if;

end process;

-- end architecture

In deze twee voorbeelden is er in de beschrijving gezorgd dat voor alle mogelijkheden een waarde beschikbaar is. Het eerste voorbeeld doet dit expliciet. Wanneer er veel uitgangen zijn, kan dit snel omslachtige worden. Het tweede voorbeeld kan dan een oplossing vormen, door eerst default waardes toe te kennen aan alle uitgangen.

-- entity

-- architecture

signal getal : STD_LOGIC_VECTOR(3 downto 0);

signal getal_is_even, getal_is_oneven : STD_LOGIC;

-- begin

PMUX: process(getal)

begin

getal_is_oneven <= '0';

getal_is_even <= '0';

if getal(0) = '1' then

getal_is_oneven <= '1';

elsif getal(0) = '0' then

getal_is_even <= '1';

end if;

end process;

-- end architecture

Power to the editor

VHDL is een expliciete taal. Er moet veel code geschreven worden, als we het aantal “karakters” tellen in een beschrijving.

Tegenwoordig bestaan er tal van general purpose editors. Aangezien VHDL-bestanden gewone tekstbestanden zijn, kunnen deze ook perfect in een editor geschreven worden. Voorbeelden van editors zijn: Visual Studio Code, Sublime, Notepad++ en UltraEdit. De meeste editors laten toe om te werken met snippets. Dit zijn onderdelen in de editor die stukken boilerplate code genereren.

Dit is een voorbeeld van een snippet in VS Code. Wanneer er in een .vhd file gewerkt wordt, zal de prefix srff meteen de block code genereren voor een SR-FlipFlop.

Het loont écht de moeite om jezelf goed vertrouwd te maken met 1 editor. Dit soort algemene editors kunnen immers gebruikt worden voor veel talen die je zal gebruiken: Python, VHDL, C, Java, Assembly (😃), HTML, CSS, …

"VHDL SRFF": {

"prefix": "srff",

"body" : [

"-- signal $1, $1_set, $1_reset : STD_LOGIC;",

"$1_set <= ;",

"$1_reset <= ;",

"PSRFF: process(clock_i)",

"begin",

" if rising_edge(clock_i) then",

" if reset_n_i = '0' then ",

" $1 <= '0';",

" else",

" if $1_reset = '1' then ",

" $1 <= '0';",

" elsif $1_set = '1' then ",

" $1 <= '1';",

" end if;",

" end if;",

" end if;",

"end process;"

],

"description": "VHDL boilerplate code for a set-reset flip-flop"

}