Sommige studenten hebben misschien al door dat de componenten tot hiertoe niet goed schaalbaar zijn. Wat als er nu nood is aan een 6-bit XOR poort? Moeten we dan voor iedere mogelijke breedte een nieuwe component maken? Nee! Dit kunnen we oplossen door generics te gebruiken. Als voorbeeld hebben we een 8-bit AND poort die generic is en kan schalen.

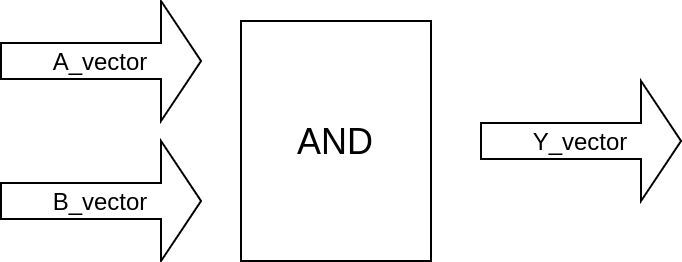

Generic AND voorstelling

Je kan deze AND poort beschrijven met onderstaand code. De variable N wordt gebruikt als het aantal inputs.

--------------------------------------------------------------------------------

-- KU Leuven - ESAT/COSIC - Emerging technologies, Systems & Security

--------------------------------------------------------------------------------

-- Module Name: nbit_and - Behavioural

-- Project Name: Digitale eletronische schakelingen

-- Description: n-bit AND poort ter illustratie van het gebruik van generics

--

-- Revision Date Author Comments

-- v0.1 20240119 VlJo Initial version

--

--------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity nbit_and is

Generic(

G_WIDTH : integer := 8

);

Port (

A_vector: in std_logic_vector(G_WIDTH-1 downto 0);

B_vector: in std_logic_vector(G_WIDTH-1 downto 0);

Z_vector: out std_logic_vector(G_WIDTH-1 downto 0)

);

end nbit_and;

architecture Behavioral of nbit_and is

-- (DE-)LOCALISING IN/OUTPUTS

signal A_vector_i : std_logic_vector(G_WIDTH-1 downto 0);

signal B_vector_i : std_logic_vector(G_WIDTH-1 downto 0);

signal Z_vector_o : std_logic_vector(G_WIDTH-1 downto 0);

begin

--------------------------------

-- (DE-)LOCALISING IN/OUTPUTS

--------------------------------

A_vector_i <= A_vector;

B_vector_i <= B_vector;

Z_vector <= Z_vector_o;

--------------------------------

-- COMBINATORIAL

--------------------------------

Z_vector_o <= A_vector_i AND B_vector_i;

end Behavioral;

Voor integers wordt er := gebruikt in VHDL.

Als we dergelijk beschreven AND poort willen gebruiken, kunnen we de G_WIDTH waarde aanpassen. In dit voorbeeld wordt de nbit_and component twee maal geïnstantieerd: een keer op 4 en een keer op 91.

...

architecture Behavioral of demo is

component nbit_and is

Generic(

G_WIDTH : integer := 8

);

Port (

A_vector: in std_logic_vector(G_WIDTH-1 downto 0);

B_vector: in std_logic_vector(G_WIDTH-1 downto 0);

Z_vector: out std_logic_vector(G_WIDTH-1 downto 0)

);

end component nbit_and;

...

begin

mijn_4_bit_and_poort: component nbit_and

generic map( G_WIDTH => 4)

port map ( A_vector => een_vier_bit_a,

B_vector => een_vier_bit_b,

Z_vector => een_vier_bit_z);

...

mijn_91_bit_and_poort: component nbit_and

generic map( G_WIDTH => 91)

port map ( A_vector => een_eenennegentig_bit_a,

B_vector => een_eenennegentig_bit_b,

Z_vector => een_eenennegentig_bit_z);

...

end Behavioral;