Zoals bij voorgaande opdrachten, wordt ook bij deze opdracht een testbench voorzien.

Het “programma” dat in de firmware staat zorgt dat er een waarde in een register geschreven wordt en dat dit horizontaal heen en weer loopt. Het programma is op zo een manier geschreven dat het bestaat uit 64 instructies. Dit heeft tot effect dat enkel de 8 LSBs van de 32-bit program counter bepalen welke instructie uitgevoerd wordt.

Daardoor zal, bij de overgang van 1111'1100 naar 1'0000'0000, het programma in een oneindige loop komen.

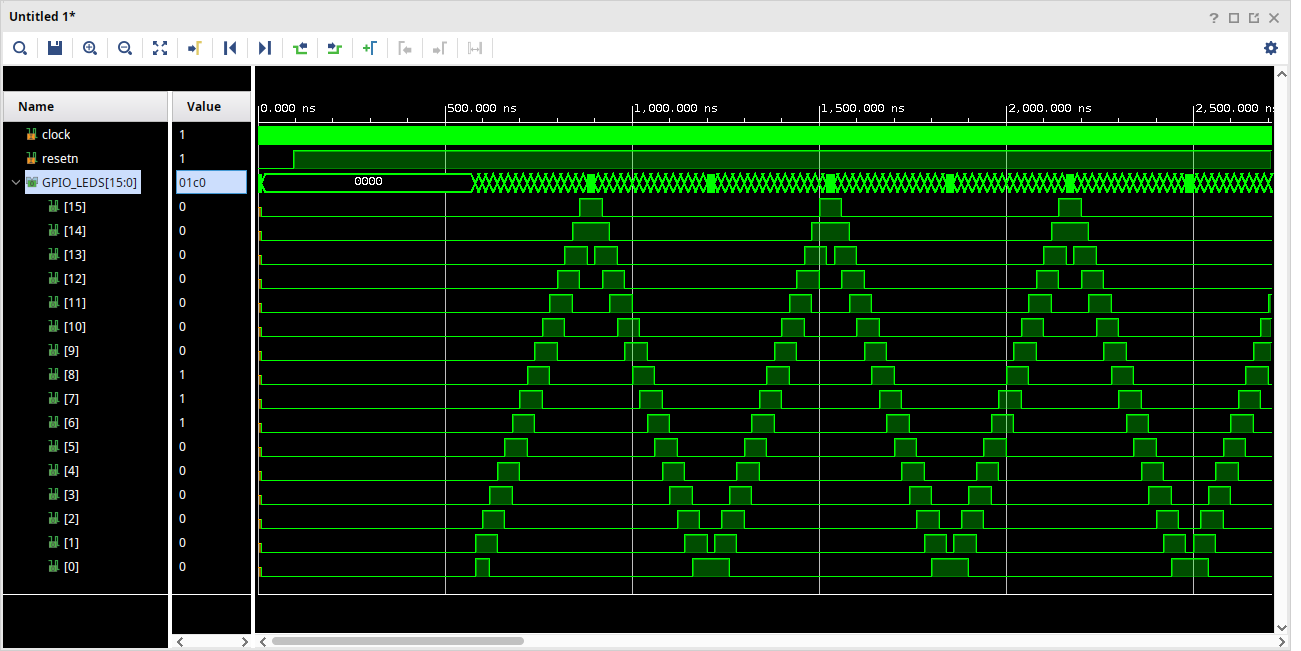

Wanneer dit programma gesimuleerd wordt, zien de waveforms er uit zoals in onderstaande figuure. Het programma zelf staat, louter ter info, onderaan deze pagina en is geschreven in assembly.

.global start

.section .init, "ax"

start:

addi x1, x0, 7

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

slli x1, x1, 1

sw x1, 0(x0)

srai x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

srli x1, x1, 1

sw x1, 0(x0)

end: