Signalen vs. variabelen

Signalen:

- nemen de nieuwe waarde aan na een vertraging,

- hebben een hardware equivalent,

- worden toegekend met " <=" .

Variabelen:

- nemen de nieuwe waarde onmiddellijk aan,

- hebben géén hardware equivalent,

- worden toegekend met " :=" ,

- komen enkel voor in een proces.

Signalen

Volgende beschrijvingen leiden tot dezelfde implementatie:

architecture arch of vb1 is

signal o1, o2, o3: std_logic;

begin

p: process(a, b, c, d, o1, o2, o3)

begin

q <= not o3;

o1 <= a and b;

o2 <= c and d;

o3 <= o1 or o2;

end process;

end arch;

architecture arch of vb2 is

signal o1, o2, o3: std_logic;

begin

q <= not o3;

o1 <= a and b;

o2 <= c and d;

o3 <= o1 or o2;

end arch;

architecture arch of vb3 is

begin

q <= not ((a and b) or (c and d));

end arch;

Als we de tussenliggende signalen o1, o2 en o3 vergeten in de sensitivity list, is het gedrag niet meer zuiver combinatorisch. Volgend proces leidt dus niet tot dezelfde implementatie als de vorige voorbeelden:

architecture arch of vb4 is

signal o1, o2, o3: std_logic;

begin

p: process(a, b, c, d)

begin

q <= not o3;

o1 <= a and b;

o2 <= c and d;

o3 <= o1 or o2;

end process;

end arch;

Resolutie-functie

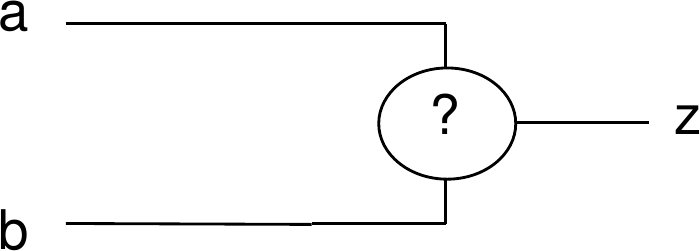

In het volgende voorbeeld worden er twee toekenningen gedaan aan hetzelfde signaal:

signal a, b, z: std_logic;

...

z <= a;

z <= b;

De resolutie functie die voorzien is in het type std_logic maakt een keuze tussen a en b op basis van de waarde van a en b.

De resolutie-functie sluit niet uit dat de synthesetool (die de code omzet in hardware) een foutmelding kan geven.

Variabelen

Als we variabelen gebruiken in plaats van signalen, krijgen we opnieuw dezelfde implementatie:

architecture arch of vb5 is

begin

p: process(a, b, c, d)

variable o1, o2, o3;

begin

q <= not o3;

o1 := a and b;

o2 := c and d;

o3 := o1 or o2;

end process;

end arch;

Voor code die hardware beschrijft (a.k.a. synthetiseerbare code) gebruiken we std_logic.

In een testbench kunnen we wel variabelen gebruiken.