Zoals er eerder al aangehaald worden alle componenten tegelijkertijd uitgevoerd. Net zoals op een breadboard, zijn alle componenten en poorten gelijktijdig actief. Wanneer het ontwerp complexer wordt, is het bijna onmogelijk om iets realiseren als er geen orde of volgorde is. Hiervoor is het klok-signaal ontstaan. Dit signaal speelt een soortgelijke rol zoals die van een dirigent bij een concert.

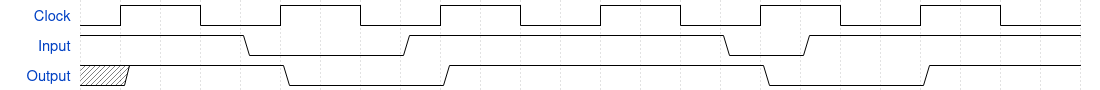

Als we bij combinatorische logica de ingang veranderen, duurt het een zekere tijd voordat dat de uitgang (mogelijks) verandert. Bij sequentiële logica gaan we wachten met de ingang in te lezen tot de stijgende flank van de clock. Als de timings van het design goed zijn dan is de ingang van een systeem altijd stabiel op het moment dat er een stijgende flank van een clock is.

We gaan beginnen met een simpele D flip-flop te maken. Het enige dat deze flip-flop doet is de ingang onthouden op de uitgang tot de volgende stijgende flank van de clock.

Symbool van een D-flipflop

Timing van een D-flipflop

Onderstaande vhdl code is een voorbeeld van een flip-flop. Het is hier belangrijk om te zien dat bij het process alleen de clock in de sensitivity list zit. Ook al zou jouw buikgevoel zeggen “Jamaar, als de input wijzigt moet ook de inhoud van de flipflop wijzigen!!” … toch is dit géén reden om die input in de sensitivity list te zetten. Het enige moment dat er gesampled mag worden, is als de dirigent het zegt. In dit geval is dat op de rising edge van de het kloksignaal.

--------------------------------

-- Revision Date Author Comments

-- v0.1 20240122 VlJo Initial version

--------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity D_flipflop is

Port (

clock: in std_logic;

D: in std_logic;

Q: out std_logic);

end D_flipflop;

architecture Behavioral of D_flipflop is

signal clock_i : std_logic;

signal D_i : std_logic;

signal Q_o : std_logic;

begin

--------------------------------

-- (DE-)LOCALISING IN/OUTPUTS

--------------------------------

clock_i <= clock;

D_i <= D;

Q <= Q_o;

--------------------------------

-- SEQUENTIAL

--------------------------------

SEQ: process(clock_i)

begin

if rising_edge(clock_i) then

Q_o <= D_i;

end if;

end process;

end Behavioral;

Een alternatief voor if rising_edge(clock_i) then is if clock_i'event and clock_i = '1' then.