Om een beschrijving te maken van de behandelde FSM in VHDL, wordt er weer gebruikt gemaakt van een opsommingstype. Vervolgens worden er 2 signalen aangemaakt van dit nieuw-gemaakte type:

type T_demo_fsm_states is (sReset, sGroen, sOranje, sRood);

signal current_state, next_state: T_demo_fsm_states;

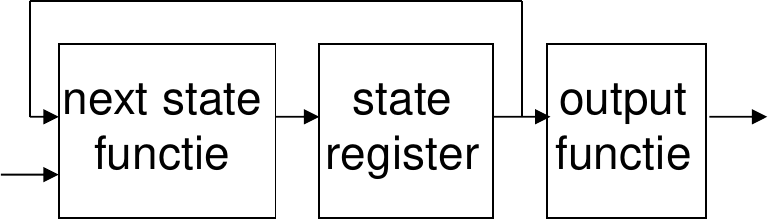

Met deze twee signalen gedefinieerd en gedeclareerd, is het terug business-as-usual. Er is een tekening van het ontwerp, dus rest er enkel nog om hier een beschrijving van te maken.

- register voor het state-register: ✔

- multiplexer voor de output functie: ✔

- combinatorisch voor de next-state functie: ✔

Moore FSM

Next state function

PFSM_NSF: process(current_state, halt)

begin

case current_state is

when sGroen =>

next_state <= sOranje;

when sOranje =>

next_state <= sRood;

when others =>

if halt = '1' then

next_state <= sReset;

else

next_state <= sGroen;

end if;

end case;

end process;

State register

PFSM_REG: process(clock_i)

begin

if rising_edge(clock_i) then

if reset_i = '1' then

current_state <= sReset;

else

current_state <= next_state;

end if;

end if;

end process;

Output function

PFSM_OF: process(current_state)

begin

groen_o <= '0';

oranje_o <= '0';

rood_o <= '0';

case current_state is

when sRood => rood_o <= '1';

when sOranje => oranje_o <= '1';

when sGroen => groen_o <= '1';

when others => groen_o <= '1';

oranje_o <= '1';

rood_o <= '1';

end case;

end process;